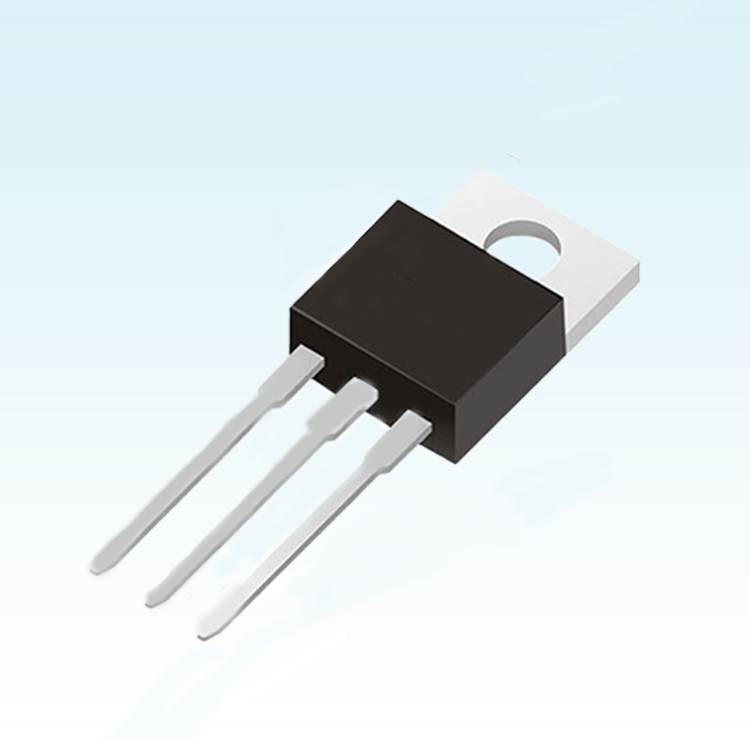

铜陵MOSFET二极管联系方式

工作原理

截止:漏源极间加正电源,栅源极间电压为零。P基区与N漂移区之间形成的PN结J1反偏,漏源极之间无电流流过。

导电:在栅源极间加正电压UGS,栅极是绝缘的,所以不会有栅极电流流过。但栅极的正电压会将其下面P区中的空穴推开,而将P区中的少子—电子吸引到栅极下面的P区表面

当UGS大于UT(开启电压或阈值电压)时,栅极下P区表面的电子浓度将超过空穴浓度,使P型半导体反型成N型而成为反型层,该反型层形成N沟道而使PN结J1消失,漏极和源极导电。

功率MOSFET的设计过程中采取措施使其中的寄生晶体管尽量不起作用。在不同代功率MOSFET中其措施各有不同,但总的原则是使漏极下的横向电阻RB尽量小。因为只有在漏极N区下的横向电阻流过足够电流为这个N区建立正偏的条件时,寄生的双极性晶闸管才开始发难。然而在严峻的动态条件下,因dv/dt通过相应电容引起的横向电流有可能足够大。此时这个寄生的双极性晶体管就会起动,有可能给MOSFET带来损坏。所以考虑瞬态性能时对功率MOSFET器件内部的各个电容(它是dv/dt的通道)都予以注意。瞬态情况是和线路情况密切相关的,这方面在应用中应给予足够重视。对器件要有深入了解,才能有利于理解和分析相应的问题。

FET用作具有两个触点的导电半导体通道-“源极”和漏极。 GATE结可以被理解为作为MOS结构的2端子电路,该MOS结构用作整流反向偏置模式。 通常,在经典工作情况下,GATE阻抗较高。根据这些标准的FET通常是MOSFET,JFET,金属半导体FET(MESFET)和异质结构FET。 在这些FET中,MOSFET是重要的晶体管之一,通常用于各种应用。

在硅基MOSFET中,GATE端子通常由特定的SiO2层绝缘。 导电通道的电荷载流子产生相反的电荷,在这种情况下,n通道为e型p型衬底,p通道为n型衬底“空穴”。 这将通过在GATE端子上施加电压在硅绝缘体边缘的半导体中感应到。 e-将进入和离开n +源极和漏极端子的通道,此通道为n通道金属氧化物半导体场效应晶体管。 在p型金属氧化物半导体场效应晶体管期间,这将是p +触点。

作为多数载流子器件,MOSFET在其源极和漏极之间承载电流。 该晶体管通过施加到相应 MOS 栅极的常规电压进行调节。 在 n-MOSFET中,电子充当多数载流子,而在 p-MOSFET中,空穴充当多数载流子。

为了正常工作,MOSFET 保持正温度系数。这意味着几乎没有热失控的机会。通态损耗较低,因为理论上晶体管的通态电阻没有限制。此外,由于 MOSFET 可以在高频下工作,它们可以执行快速开关应用而关断损耗很小。